对Allegro使用熟练程度,不仅在使用上,还要知道如何进行阻抗控制,如何使用工具进行信号完整性分析.如何使用IBIS模型。真正的PCB高手应该还是信号完整性专家。(在我面试过程中也经常会被询问到是否对高速板进行仿真的问题)。 对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题。

PCB设计者,很注重叠层问题,一个好的叠层结构是对大多数信号整体性问题和EMC问题的最好防范措施,同时也最易被人们误解。这里有几种因素在起作用,能解决一个问题的好方法可能会导致其它问题的恶化。很多系统设计供应商会建议电路板中至少应该有一个连续平面以控制特性阻抗和信号质量,只要成本能承受得起,这是个很好的建议。

EMC咨询专家时常建议在外层上放置地线填充(ground fill)或地线层来控制电磁辐射和对电磁干扰的灵敏度,在一定条件下这也是一种好建议。

然而,由于瞬态电流的原因,在某些普通PCB设计中采用这种方法可能会遇到麻烦。首先,我们来看一对电源层/地线层这种简单的情况:它可看作为一个电容。可以认为电源层和地线层是电容的两个极板。要想得到较大的电容值,就需将两个极板靠得更近(距离D),并增大介电常数(εr)。

电容越大则阻抗越低,这是我们所希望的,因为这样可以抑制噪声。不管其它层怎样安排,主电源层和地线层应相邻,并处于叠层的中部。如果电源层和地线层间距较大,就会造成很大的电流环并带来很大的噪声。

PCB的各层分布一般是对称的。不应将多于两个的信号层相邻放置;否则,很大程度上将失去对SI的控制。最好将内部信号层成对地对称放置。除非有些信号需要连线到SMT器件,我们应尽量减少外层的信号布线。

层的排布一般原则:

1)元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;

2)所有信号层尽可能与地平面相邻;

3)尽量避免两信号层直接相邻;

4)主电源尽可能与其对应地相邻;

5)兼顾层压结构对称。

6)对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在50MHZ以上的(50MHZ以下的情况可参照,适当放宽),建议排布原则:

7)元件面、焊接面为完整的地平面(屏蔽);

8)无相邻平行布线层;

9)所有信号层尽可能与地平面相邻;

10)关键信号与地层相邻,不跨分割区。

注:具体PCB的层的设置时,要对以上原则进行灵活掌握,在领会以上原则的基础上,根据实际单板的需求,如:是否需要一关键布线层、电源、地平面的分割情况等,确定层的排布,切忌生搬硬套,或抠住一点不放。

四层板:优选方案1,可用方案3

方案 电源层数/地层数/信号层数 1/2/3/4

#1 1 1 2 S G P S

#2 1 2 2 G S S P

#3 1 1 2 S P G S

方案1 此方案四层PCB的主选层设置方案,在元件面下有一地平面,关键信号优选布TOP层;至于层厚设置,有以下建议:

满足阻抗控制芯板(GND到POWER)不宜过厚,以降低电源、地平面的分布阻抗;保证电源平面的去藕效果;为了达到一定的屏蔽效果,有人试图把电源、地平面放在TOP、BOTTOM层,即采用方案2:此方案为了达到想要的屏蔽效果,至少存在以下缺陷:电源、地相距过远,电源平面阻抗较大;电源、地平面由于元件焊盘等影响,极不完整由于参考面不完整,信号阻抗不连续。

实际上,由于大量采用表贴器件,对于器件越来越密的情况下,本方案的电源、地几乎无法作为完整的参考平面,预期的屏蔽效果很难实现;方案2使用范围有限。但在个别单板中,方案2不失为最佳层设置方案。

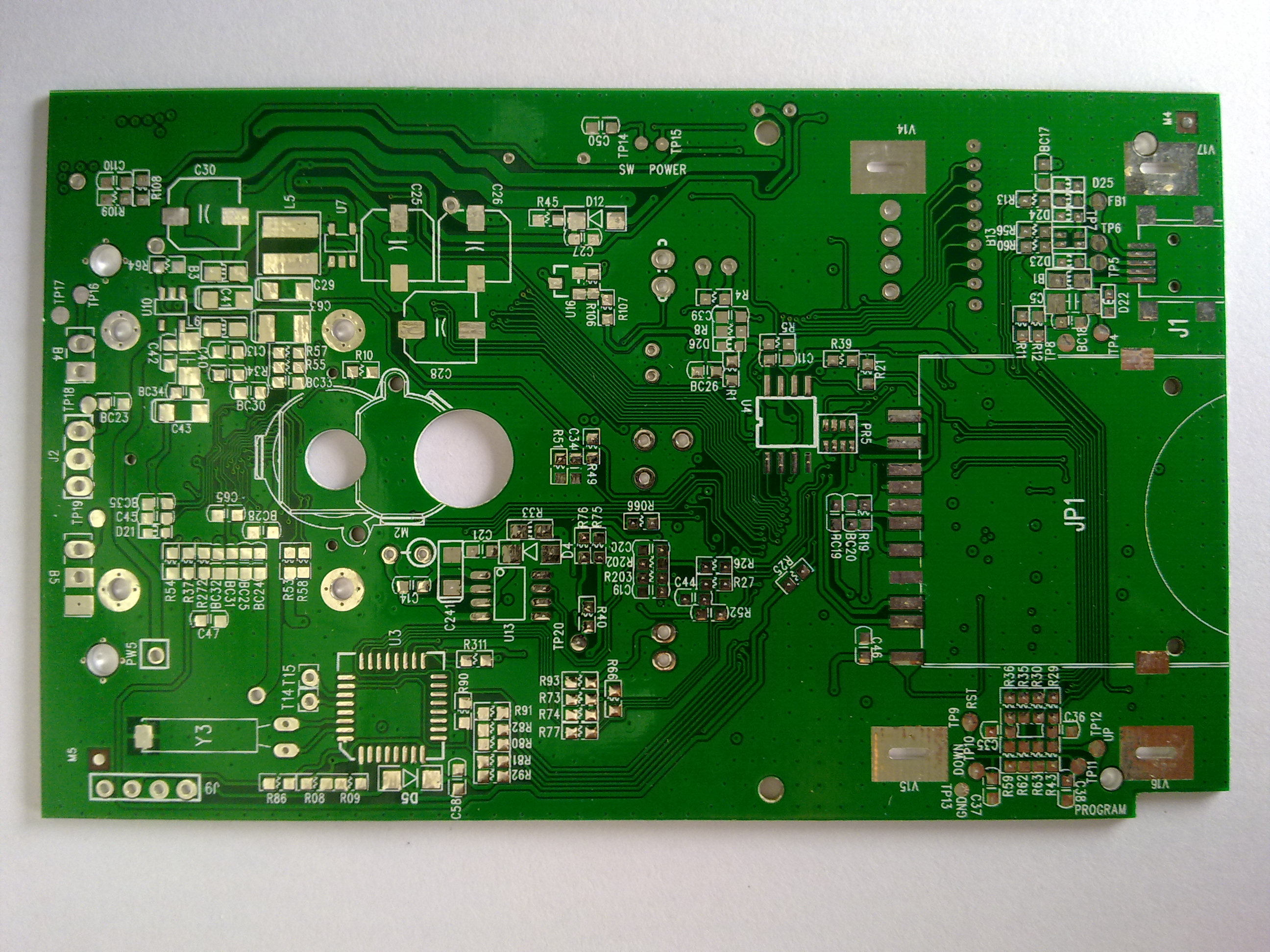

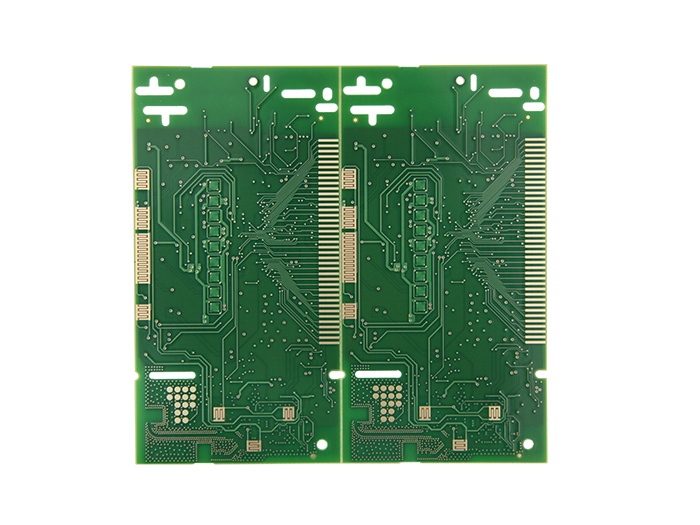

以下为方案2使用案例;

案例(特例):设计过程中,出现了以下情况:

A、整板无电源平面,只有GND、PGND各占一个平面;

B、整板走线简单,但作为接口滤波板,布线的辐射必须关注;

C、该板贴片元件较少,多数为插件。

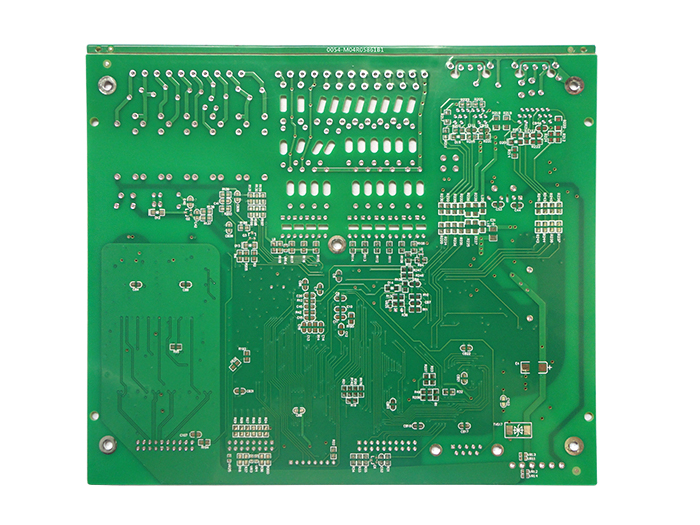

分析:

1、由于该板无电源平面,电源平面阻抗问题也就不存在了;

2、由于贴片元件少(单面布局),若表层做平面层,内层走线,参考平面的完整性基本得到保证,而且第二层可铺铜保证少量顶层走线的参考平面;

3、作为接口滤波板,PCB布线的辐射必须关注,若内层走线,表层为GND、PGND,走线得到很好的屏蔽,传输线的辐射得到控制;

鉴于以上原因,在本板的层的排布时,决定采用方案2,即:GND、S1、S2、PGND,由于表层仍有少量短走线,而底层则为完整的地平面,我们在S1布线层铺铜,保证了表层走线的参考平面;五块接口滤波板中,出于以上同样的分析,设计人员决定采用方案2,同样不失为层的设置经典。

方案3:此方案同方案1类似,适用于主要器件在BOTTOM布局或关键信号底层布线的情况;一般情况下,限制使用此方案;

六层板:优选方案3,可用方案1,备用方案2、4

方案 电源 地 信号 1/2/3/4/5/6

#1 1 1 4 S1 G S2 S3 P S4

#2 1 1 4 S1 S2 G P S3 S4

#3 1 2 3 S1 G1 S2 G2 P S3

#4 1 2 3 S1 P G1 S2 G2 S3

对于六层板,优先考虑方案3,优选布线层S2(stripline),其次S3、S1。主电源及其对应的地布在4、5层,层厚设置时,增大S2-P之间的间距,缩小P-G2之间的间距(相应缩小G1-S2层之间的间距),以减小电源平面的阻抗,减少电源对S2的影响;

在成本要求较高的时候,可采用方案1,优选布线层S1、S2,其次S3、S4,与方案1相比,方案2保证了电源、地平面相邻,减少电源阻抗,但S1、S2、S3、S4全部裸露在外,只有S2才有较好的参考平面;

对于局部少量信号要求较高的场合,方案4比方案3更适合,它能提供极佳的布线层S2。

八层板:优选方案2、3、可用方案1

方案 电源 地 信号 1 2 3 4 5 6 7 8

#1 1 2 5 S1 G1 S2 S3 P S4 G2 S5

#2 1 3 4 S1 G1 S2 G2 P S3 G3 S4

#3 2 2 4 S1 G1 S2 P1 G2 S3 P2 S4

#4 2 2 4 S1 G1 S2 P1 P2 S3 G3 S4

#5 2 2 4 S1 G1 P1 S2 S3 G2 P2 S4

对于单电源的情况下:

方案2比方案1减少了相邻布线层,增加了主电源与对应地相邻,保证了所有信号层与地平面相邻,代价是:牺牲一布线层;

对于双电源的情况:

推荐采用方案3,方案3兼顾了无相邻布线层、层压结构对称、主电源与地相邻等优点,但S4应减少关键布线;

方案4:无相邻布线层、层压结构对称,但电源平面阻抗较高;应适当加大3-4、5-6,缩小2-3、6-7之间层间距;

方案5:与方案4相比,保证了电源、地平面相邻;但S2、S3相邻,S4以P2作参考平面;对于底层关键布线较少以及S2、S3之间的线间窜扰能控制的情况下此方案可以考虑;

如果对一个8层板,将电源层放在一侧而将地线层放在另一侧,将会导致如下问题:

1、最大的串扰。由于交互电容增大,各信号层之间的串扰比各层本身的串扰还大。

2、最大的环流。电流围绕各电源层流动且与信号并行,大量电流进入主电源层并通过地线层返回。EMC特性会由于环流的增大而恶化。

3、失去对阻抗的控制。信号离控制层越远,由于周围有其它导体,因此阻抗控制的精度就越低。

4、由于容易造成焊锡短路,可能会增加产品的成本。

我们必须在性能和成本之间进行折衷选择

十层板:

1)S-G-S-S-G-P-S-S-G-S 单电源

2)S/P/S/G/S/S/

推荐方案2、3、可用方案1、4

方案3:扩大3-4与7-8各自间距,缩小5-6间距,主电源及其对应地应置于6、7层;优选布线层S2、S3、S4,其次S1、S5;本方案适合信号布线要求相差不大的场合,兼顾了性能、成本;推荐大家使用;但需注意避免S2、S3之间平行、长距离布线;

方案4:EMC效果极佳,但与方案3比,牺牲一布线层;在成本要求不高、EMC指标要求较高、且必须双电源层的关键单板,建议采用此种方案;优选布线层S2、S3,对于单电源层的情况,首先考虑方案2,其次考虑方案1。方案1具有明显的成本优势,但相邻布线过多,平行长线难以控制;

十二层板:推荐方案2、3,可用方案1、4、备用方案5

方案2、4具有极好的EMC性能,方案1、3具有较佳的性价比;

以上层排布作为一般原则,仅供参考,具体设计过程中大家可根据需要的电源层数、布线层数、特殊布线要求信号的数量、比例以及电源、地的分割情况,结合以上排布原则灵活掌握。

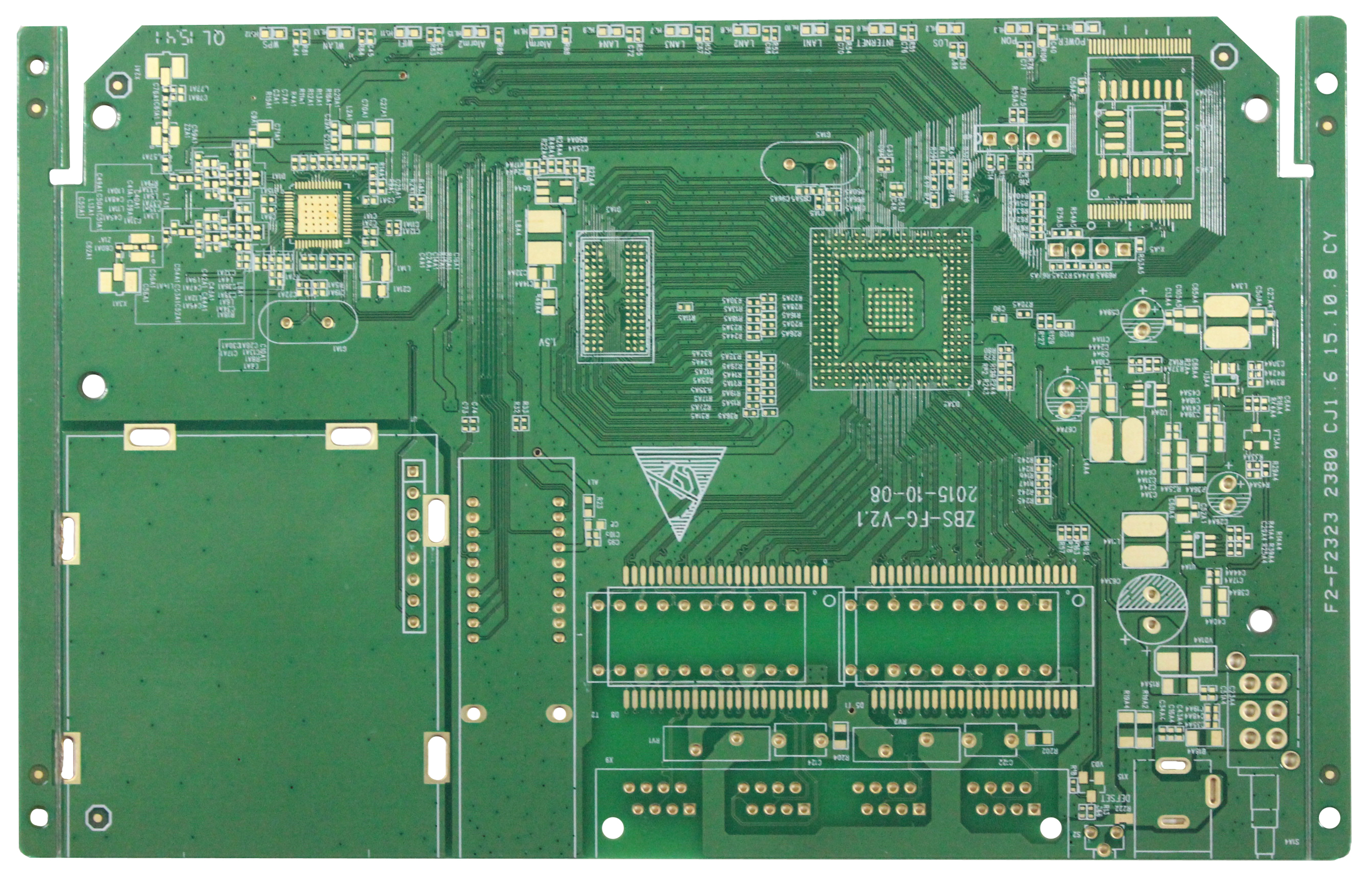

其他资料:常用多层PCB叠层设计配置

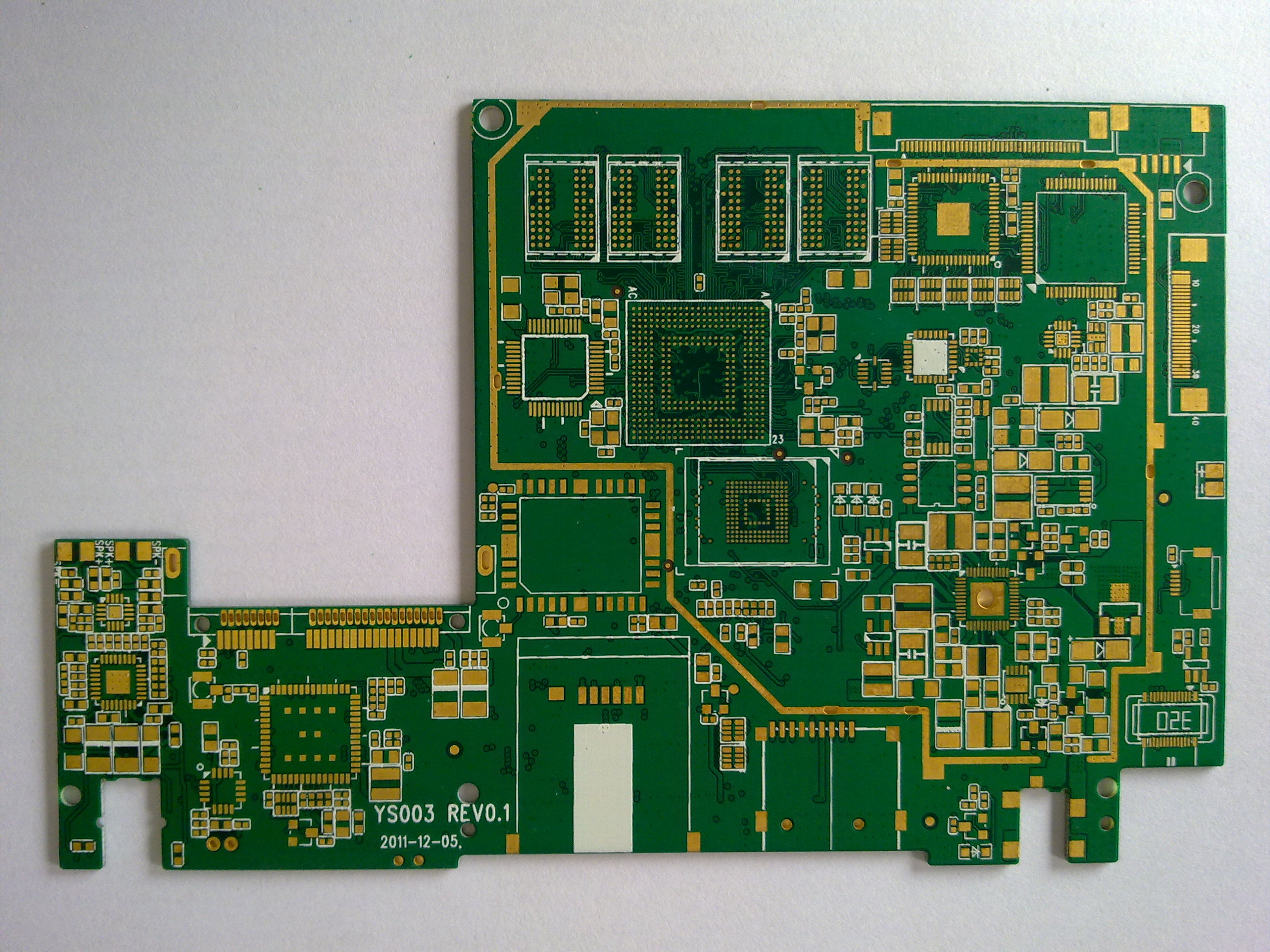

core和pp从本质上讲是一类东西,他们都是电介质。core又叫内芯板,是两面带铜箔的;pp的英文是prepreg,也叫预浸或半固化片。pp就是单纯的介质。制作多层板时,Core和PP配合使用的,CORE与CORE之间用PP粘合,CORE厚度(含铜皮)有0.2mm/0.3mm/0.4mm/0.5mm/0.6mm/0.8mm/1.0mm/1.1mm/1.2mm/1.6mm/1.9mm ,PP和core相比要软一些,并且有一定的粘性,它有很多种厚度可供选择,以便对电路板的叠层厚度进行调整以达到控制阻抗的目的。PP厚度有106/1080/2116/7628。

1. 确定PCB板叠层结构

2. 从PCB厂家获得工艺能力参数

常用半固化片规格 | 7628(0.185mm),2116(0.105mm)1080(0.075mm) 3313(0.095mm) | 括号内为生益半固化片压合后厚度的理论平均值 |

最小导线宽度 | 4mil(对18um、35um的基铜) | 局部区域非BGA、SMT区时需评审 |

最小导线间距 | 4mil(允许局部3.5mil)(对18um、35um的基铜) | 局部区域非BGA、SMT区时需评审 |

最小导线宽与间距 | 5/7mil(2oz的基铜) | |

最小线到盘、盘到盘间距 | 3.5mil(18 um ,35 um),5 mil(70 um) | 此极限时线路与焊盘均无法补偿 |

3. 从厂家获得多层板叠层结构,用以确定半固化片pp和core的叠层方案,通常情况下从top到bottom叠层方案如下:pp-core-pp-core-pp-core-pp…-pp。

4. 根据自身设计中所用器件封装及器件特性情况,再结合上表中所列出的最小线宽,间距等参数确定各层走线的width,差分线的width、gap等参数,width、gap等参数设定完成之后,就需要考虑阻抗匹配问题。

5. 阻抗的计算需要借助工具,通常用allegro自身带的计算工具,但如果用盗版的话计算参数不一定准确,推荐使用polar。

6. 有了线宽、间距和介电常数,就可以综合考虑copper厚度、core的厚度、pp的厚度等参数。